# Deliverable 4.1

## **Report on Co-Engineering Process Support**

This project has received funding from the Electronic Component Systems for European Leadership Joint Undertaking under grant agreement No 737475. This Joint Undertaking receives support from the European Union's Horizon 2020 research and innovation programme and Spain, France, United Kingdom, Austria, Italy, Czech Republic, Germany.

The author is solely responsible for its content, it does not represent the opinion of the European Community and the Community is not responsible for any use that might be made of data appearing therein.

| DISSEMINATION LEVEL |    |                                                                                      |  |  |  |

|---------------------|----|--------------------------------------------------------------------------------------|--|--|--|

| Х                   | PU | Public                                                                               |  |  |  |

|                     | со | Confidential, only for members of the consortium (including the Commission Services) |  |  |  |

| COVER AND CONTROL PAGE OF DOCUMENT |                                                                                                                              |  |  |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Project Acronym:                   | AQUAS                                                                                                                        |  |  |  |  |

| Project Full Name:                 | Aggregated Quality Assurance in Systems                                                                                      |  |  |  |  |

| Grant Agreement No.:               | 737475                                                                                                                       |  |  |  |  |

| Programme                          | ICT-1: Cyber-Physical-Systems                                                                                                |  |  |  |  |

| Instrument:                        | Research & innovation action                                                                                                 |  |  |  |  |

| Start date of project:             | 01.05.2017                                                                                                                   |  |  |  |  |

| Duration:                          | 36 months                                                                                                                    |  |  |  |  |

| Deliverable No.:                   | D4.1                                                                                                                         |  |  |  |  |

| Document name:                     | Report on co-engineering process support                                                                                     |  |  |  |  |

| Work Package                       | WP4                                                                                                                          |  |  |  |  |

| Associated Task                    | Task 4.1                                                                                                                     |  |  |  |  |

| Nature <sup>1</sup>                | R                                                                                                                            |  |  |  |  |

| Dissemination Level <sup>2</sup>   | PU                                                                                                                           |  |  |  |  |

| Version:                           | 0.1                                                                                                                          |  |  |  |  |

| Actual Submission Date:            | 24-05-2018                                                                                                                   |  |  |  |  |

| Contractual Submission Date        | 30-04-2018                                                                                                                   |  |  |  |  |

| Editor:<br>Institution:<br>E-mail: | Christian Fuss / Mario Winkler<br>ANSYS medini Technologies AG<br><u>christian.fuss@ansys.com</u><br>mario.winkler@ansys.com |  |  |  |  |

<sup>&</sup>lt;sup>2</sup> **PU**=Public, **CO**=Confidential, only for members of the consortium (including the Commission Services)

<sup>&</sup>lt;sup>1</sup> **R**=Report, **DEC**= Websites, patents filling, etc., **O**=Other

## Change Control

### **Document History**

| Version | Date       | Change History                                        | Author(s)  | Organisation(s) |

|---------|------------|-------------------------------------------------------|------------|-----------------|

| 0.1     | 06.09.2017 | Initial draft of document structure                   | C. Fuss    | AMT             |

| 0.2     | 18.01.2018 | Revised document structure and resorted contributions | C. Fuss    | AMT             |

| 1.0     | 24.5.2018  | finalized                                             | M. Winkler | AMT             |

### **Distribution List**

| Date        | Issue                                            | Group                           |

|-------------|--------------------------------------------------|---------------------------------|

| 11.09.2017  | 0.1 Call for inputs                              | design.tooling@aquas-project.eu |

|             |                                                  | all@aquas-project.eu            |

| 26.04.2018  | 0.2 Call for additional inputs and modifications | design.tooling@aquas-project.eu |

| 2010 112010 |                                                  | all@aquas-project.eu            |

| 24.05.2018  | 1.0 Final version                                | ECSEL JU                        |

| 2           |                                                  | all@aquas-project.eu            |

## Table of Contents

| 1               | Introduction [AMT]7                                                                        |

|-----------------|--------------------------------------------------------------------------------------------|

| Structure       | e of this Document                                                                         |

| 2               | Process Model                                                                              |

| 2.1             | Meta-Model                                                                                 |

| 2.2             | Overview 10                                                                                |

| Interactio      | on Points                                                                                  |

| 3               | Use Cases                                                                                  |

| 3.1             | UC1 – Air Traffic Management [ISYS] 15                                                     |

| 3.2             | UC2 – Medical Devices [ITI]                                                                |

| 3.3             | UC3 – Rail Carriage System [ClearSy] 22                                                    |

| 3.4             | UC4 – Industrial Drive [AMT] 24                                                            |

| 3.4.1           | Process Definition                                                                         |

| Analysis I      | Phase                                                                                      |

| Realizatio      | on Phase                                                                                   |

| 3.4.2           | Tasks and Activities                                                                       |

| 3.4.3           | Methods and Tools                                                                          |

| 3.4.4           | Interaction Points                                                                         |

| 3.5             | UC5 – Space Multicore Architecture [TASE]                                                  |

| 4               | Tools                                                                                      |

| 4.1             | System Modelling and Analysis of Quality Criteria [AMT]                                    |

| 4.2             | Co-Design and Implementation of Safety and Performance [ITI]                               |

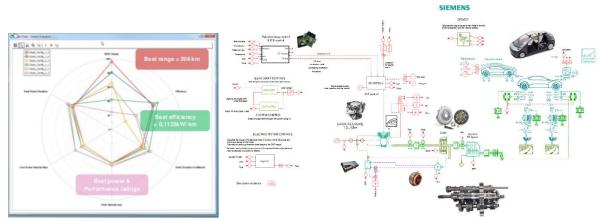

| 4.3             | Behavioural system analysis for improved SSP [SISW]                                        |

| 4.4             | Asset and Artefact Management for Co-Engineering [MDS] 40                                  |

| 4.5<br>analysis | Modelling of security requirements and properties, and verification through static code 40 |

| 4.6             | Modelling and Analysis of Co-Engineering Requirements [Intecs]                             |

| 4.7             | OPENCERT [tecnalia]                                                                        |

| 4.8             | Static and Dynamic Code Analysis in the Co-Engineering Process [BUT]                       |

| 4.9             | Safety and Security Co-engineering Including Performance [All4Tec]                         |

| 4.10            | Performance evaluation before implementation [TRT]                                         |

| 4.11<br>[TRT]   | Timing behaviour verification for Performance and Safety at early design phases safety 51  |

| 4.11.1 | Time4Sys                                                    | . 51 |

|--------|-------------------------------------------------------------|------|

| 4.11.2 | Tempo Verifier                                              | . 52 |

| 4.12   | Workflow Automation for Multi-Concern Assurance [AIT]       | . 54 |

| 4.13   | Sub-System Hardening of Communication Protocols [TrustPort] | . 58 |

| 5      | Conclusion [AMT]                                            | . 61 |

| 6      | References [all]                                            | . 62 |

## **Executive Summary**

This deliverable is the result of AQUAS task 4.1. Its roles towards supporting work in AQUAS are:

- specifying required functionalities enabling tool support of co-engineering processes according to the AQUAS methodology as it is currently understood in respect to the requirements, it will be adapted as the project progresses;

- starting the formalization of the methodology in a tool-based process model by using the Software & Systems Process Engineering Meta-Model (SPEM);

- explaining the adaptations of this methodology for the different use cases;

- outlining the partner's tools to support this methodology and especially explaining the planned extension to support the analysis of safety, security and performance properties and the foreseen interactions amongst the tools.

## 1 Introduction [AMT]

The work documented in this deliverable is based on the methodology on safety, security and performance processes that is elaborated in WP3. The AQUAS methodology will emerge from the use cases actual processes, as derived from the application of the different standards, from the emerging definitions of co-engineering and interaction points and from the application and integration of tools to support the different processes.

This report specifies required functionalities enabling tool support of co-engineering processes according to this approach. Functionalities will be described for common and global factors as well as their tool-specific implementation. Functionalities comprise tracking process progress, data and artefacts, and interactions points where cross-domain and cross disciplinary analyses must be executed to realize safety-security-performance analysis, supporting system design space exploration and trade-offs. Activities will also address ways for requirements to be linked/transferred to different tools allowing the requirement continuities in the safety, security and performance domains.

In this process, the information that should be collected in the design models for enabling this coengineering support will be considered. Beyond models and formats, data repositories and management will also be addressed.

## Structure of this Document

This document starts with a description of the tool-based process and methodology description in **Chapter 2**, contributing to Objective O6 to provide a well-defined process with clear descriptions of interactions among continuous engineering activities.

**Chapter 3** is structured along the lines of the use cases and describes the actual process planned for each use case, with a focus on interaction and tools. Using a formalized model with tools attached to tasks and tasks composed to more complex activities, allows to identify reliably all interaction between the different technologies and tools, fulfilling Objective O1.

The tools used in the use case are described with their data models and interfaces available for interaction throughout the process are presented in **Chapter 4**. This clear definition of data models and interactions can reduce the unwanted repletion, supporting Objective O7.

The document closes with a **Conclusion** and a list of **References**.

## 2 Process Model

One of the core goals of the AQUAS project is to develop a methodology for co-engineering in the product life cycle that supports qualitative and especially quantitative techniques for the analysis and assessment of safety, security and performance properties, both in separate and integrated ways. The main tasks contributing to this goal are carried out within WP3 (see deliverables D3.1).

To make this methodology accessible and allow reuse of process building blocks, it is planned to provide a tool-based process description for co-engineering processes, that enables the definition of the individual process including the work products, roles and activities but also allows to define the required synchronization among these different processes. This task is carried out within WP4 but is based on the outcomes of tasks of WP3 so far. The model shall be maintained and enhanced, as WP3 progresses.

The following sections will give an overview on the approach and outline the content.

### 2.1 Meta-Model

The process description is formalized in SPEM (Software & Systems Process Engineering Meta-Model) using the tool EPF Composer. The outcome is an EPF model and a generated website describing all parts of the process and allowing navigation through the knowledge base.

This EPF model of the AQUAS methodology is specified as an initial version and is considered as a living document. The final definition of the process phases and especially of the interaction points will be adopted according to the results that will be developed throughout the AQUAS project within the use cases.

"The Software and Systems Process Engineering Meta-model (SPEM) is a process engineering metamodel as well as conceptual framework, which can provide the necessary concepts for modeling, documenting, presenting, managing, interchanging, and enacting development methods and processes. An implementation of this meta-model would be targeted at process engineers, project leads, project and program managers who are responsible for maintaining and implementing processes for their development organizations or individual projects." [OMG-SPEM]

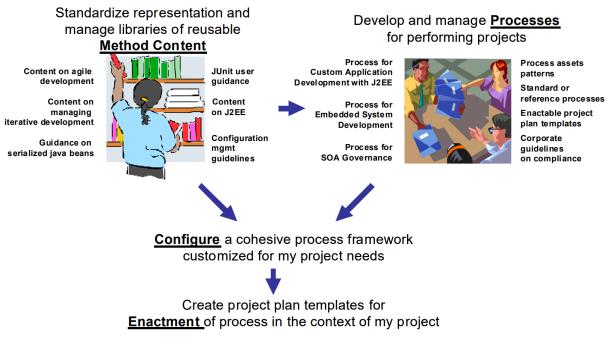

The idea of SPEM is to separate reusable method content from the described software processes which can be seen in below figure. Because of this the processes that are contained are reusable i.e. role, work products, tasks etc. This approach shall be employed for the AQUAS methodology, by describing generic content and process patterns, that can be tailored to the specific project. The viability of this approach shall be demonstrated by showcasing tailored processes for the AQUAS use cases.

Figure: Separation of reusable method content, assembly in process patterns and configuration [OMG-SPEM]

As reusable method content, the AQUAS methodology specifies tasks, that are performed by roles. A task can have input and output work products. A task can be supported by a guidance, e.g. a tool, user manual or a concept.

- Task. A unit of work a role may be asked to perform.

- **Role**. A definition of the behavior and responsibilities of an individual, or a set of individuals working together as a team.

- Work Product. A work product is a content element that represents anything used, produced, or modified by a task.

- **Guidance**. Guidance describes proven advice for accomplishing a goal. It generalizes all forms of content whose primary purpose is to provide explanations about other elements. Guidance being itself a content element, it is possible to associate guidance to other guidance.

Furthermore, the AQUAS methodology provides building blocks of the bigger process in the form of capability patterns made up of activities, which group task instances.

- **Capability Pattern**. A special process that describes a reusable cluster of activity. Capability patterns express and communicate process knowledge for a key area of interest such as a discipline and can be directly used by practitioners to guide their work.

- Activity. An activity is something that one or more roles do. It is a breakdown element which supports the nesting and logical grouping of related process elements such as descriptors (task instances) and sub-activities, thus forming breakdown structures.

The above building blocks are finally used to provide delivery processes for the use cases as examples for tailoring the AQUAS methodology and as proof of concept.

• **Delivery Process**. A delivery process is a special process describing a complete and integrated approach for performing a specific project type. It provides a complete lifecycle model that has been detailed by sequencing method content in breakdown structures.

For publication, all elements in an EPF model must be structured in categories, that build up a tree of the knowledge graph of the entities. The following kinds of categories are distinguished in EPF Composer:

- **Discipline**. A collection of related tasks that define a major 'area of concern'.

- **Domain**. An area of knowledge or activity characterized by a family of related values. A specific problem category that is characterized by a body of knowledge, activities, and behaviours. A hierarchy that groups related work products.

- Work Product Kinds. Standard category that represents a grouping of related work products which, in contrast to domain, is more presentation oriented (like models, specifications, plans, and so on).

- **Role Sets**. Used to group roles with certain commonalities together.

- **Tools**. A standard category used as a container for tool mentors. It can also provide general descriptions of the tool and its general capabilities.

- **Custom**. Used to categorize content based on user criteria. One important use is for constructing views for publication.

### 2.2 Overview

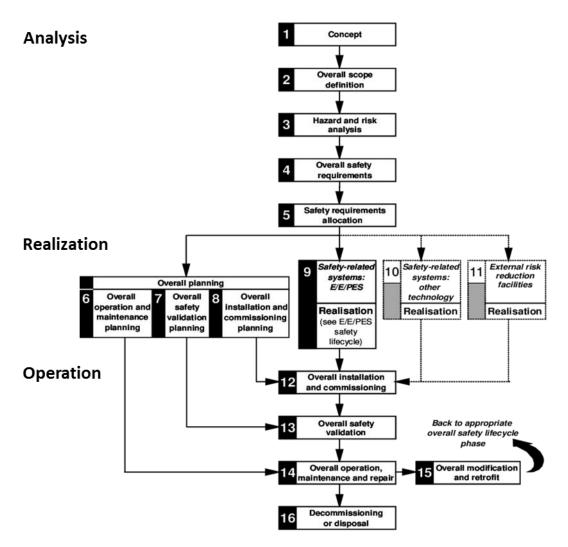

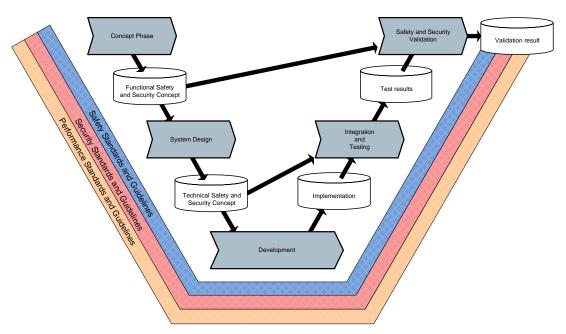

The safety life cycle model of the IEC 61508 standard provides an initial contribution to the definition of the AQUAS methodology. The SESAMO project proved that this life cycle model can well be extended to further quality criteria, like security or performance. The IEC 61508 life cycle is stage-based, below figure shows the stages.

NOTE 1 Activities relating to *verification, management of functional safety* and *functional safety assessment* are not shown for reasons of clarity but are relevent to all overall, E/E/PES and software safety lifecycle phases.

NOTE 2 The phases represented by boxes 10 and 11 are outside the scope of this standard.

NOTE 3 Parts 2 and 3 deal with box 9 (realisation) but they also deal, where relevant, with the programmable electronic (hardware and software) aspects of boxes 13, 14 and 15.

Figure: Phases of the IEC 61508 life cycle model. [IEC 61508]

**Concept.** The goal here is to gain sufficient understanding of the equipment under control (EUC) and its environment.

**Overall Scope Definition.** In this phase of the safety life-cycle, the boundaries and the relation between EUC and EUC control system (ECS) are defined, preliminary hazards are identified and the scope of the hazard and risk analysis are defined.

Hazard and Risk Analysis. Hazards at all reasonably foreseeable circumstances for EUC and ECS are determined.

**Overall Safety Requirements.** Overall safety function requirements and safety integrity requirements are defined.

**Overall Safety Requirements Allocation.** Safety functions are allocated to safety-related systems (SRS) and other risk reduction measures (ORRM).

**System Safety Requirements Specification.** System safety requirements definition (safety function requirements and system safety integrity requirements) to reach functional safety.

**Safety-Related Systems Realization.** Implementation of the SRS according to system safety-, system safety function-, and system safety integrity requirements.

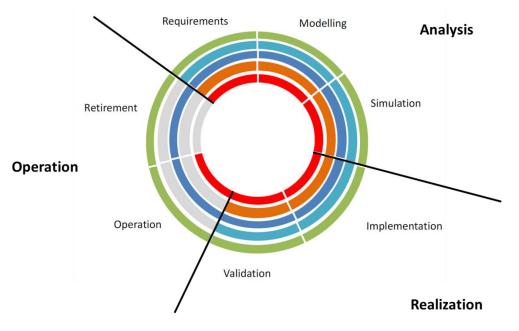

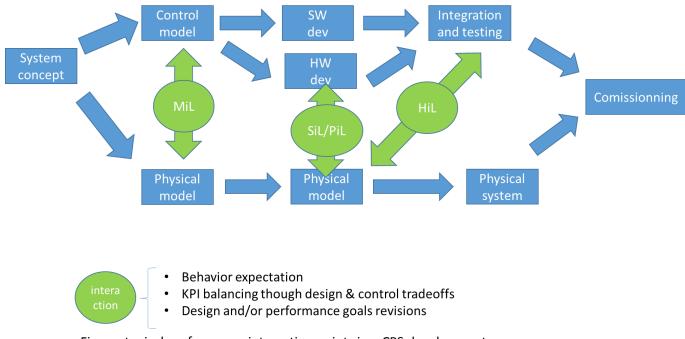

As initial approach to the AQUAS Methodology, the analysis, realization and operation stages defined in the IEC 61508 standard have mapped to a number of product life cycle areas as described in the following figure:

Figure: Stages of the AQUAS methodology

Requirements, modelling and simulation (or formal analyses) are the pre-development activity areas that constitutes the main focus of AQUAS and are expected to support also further activities during realization and operation.

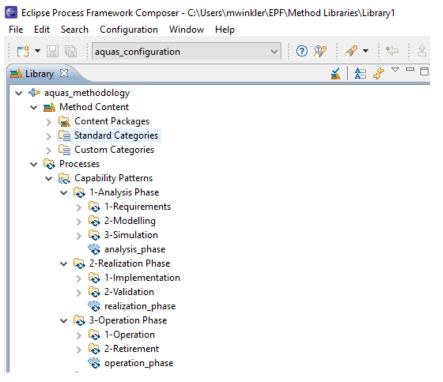

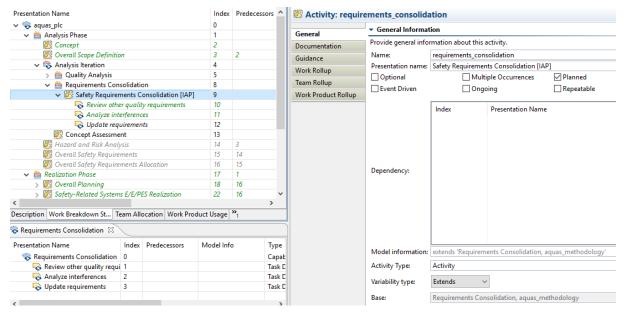

This structure is modelled as Capability Patterns in the EPF model as depicted in the following figure.

Figure: Stages modelled in the EPF Composer

Every phase in itself is structured into sub-processes that contain a set of tasks. The following figure shows this approach by using the Analysis Phase as an example.

| ^ | Presentation Name                       | Index | Predecessors        | Model Info          | Туре                |

|---|-----------------------------------------|-------|---------------------|---------------------|---------------------|

|   | ✓ S Requirements                        | 0     |                     |                     | Capability Pattern  |

|   | Scope Exploration                       | 1     |                     | extends 'scope_expl | Activity            |

|   | □ Identify Functions                    | 2     |                     |                     | Task Descriptor     |

|   | ldentify Malfunctions                   | 3     |                     |                     | Task Descriptor     |

|   | Identify Security Violations            | 4     |                     |                     | Task Descriptor     |

|   | Hazard and Risk Analysis                | 5     |                     | extends 'hazard_an  | Activity            |

|   | ldentify Hazardous Events               | 6     |                     |                     | Task Descriptor     |

|   | Determine Safety Criticality            | 7     | 6                   |                     | Task Descriptor     |

|   | R Derive Safety Goals                   | 8     |                     |                     | Task Descriptor     |

|   | ✓                                       | 9     |                     | extends 'threat_ana | Activity            |

|   | 😽 Identify Threats                      | 10    |                     |                     | Task Descriptor     |

|   | Determine Security Criticality          | 11    | 10                  |                     | Task Descriptor     |

|   | S Derive Security Objectives            | 12    | 11                  |                     | Task Descriptor     |

|   | ✓ ♣ Requirements Derivation             | 13    |                     |                     | Iteration           |

|   | Functional Requirements Derivation      | 14    |                     | extends 'functional | Activity            |

|   | S Derive Functional System Requirements | 15    |                     |                     | Task Descriptor     |

|   | Contractional Safety Requirements       | 16    |                     |                     | Task Descriptor     |

|   | Requirements                            | 17    |                     |                     | Task Descriptor     |

|   |                                         | 18    |                     | extends 'requireme  | Activity            |

|   | 8                                       |       | <ul> <li></li></ul> | <ul> <li></li></ul> | <ul> <li></li></ul> |

Figure: Sub-processes modelled in the EPF Composer

The sub-processes include:

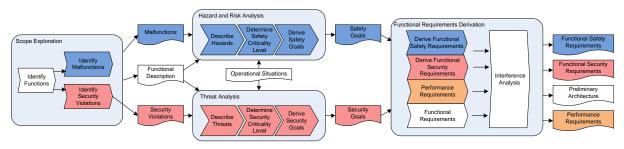

**Scope Exploration.** This is to identify the functions of your system, to identify potential malfunctioning behaviour and to explore possible violation scenarios. All these activities are modelled as Tasks in the EPF model.

**Hazard and Risk Analysis.** Here the malfunctioning behaviour is related to a relevant set of operational situations including environmental conditions and operation modes in order to determine the criticality of safety violations. Subsequently safety goals have to be derived as top-level requirements to mitigate the risk. Some aspects of performance must also be taken into account, e.g. the violation of real-time conditions.

**Threat Analysis.** Similar activities as in the Hazard and Risk Analysis are performed in respect to security. This includes the identification of potential threats, the determination of their criticality and the definition of security objectives that initiates the design to a secure system. The identified objectives have to be analysed in respect to their performance implications.

**Requirements Derivation.** Starting with the safety goals and the security objectives functional requirements for both perspectives are derived. This also includes an interference analysis defined as an Interaction Point.

#### **Interaction Points**

With its focus on co-engineering, the AQUAS methodology pays particular attention to the interaction points between the engineering of the different quality aspects, throughout the whole process. Deliverable D3.1 motivates the introduction of interaction points and describes them as both activity as well as a point in the product life cycle at which it occurs. It includes the exchange of information between experts in the different domains (e.g. safety or security). The analysis methods applied in that interaction have to be combined in order to assess various measures of interest for alternative design options. As a result decisions and recommendations have to be produced by the various experts that provide solutions for identified trade-offs between desirable properties.

Thus in the EPF Model, interaction points are modelled as capability patterns and instantiated in delivery processes or other capability patterns as activities. An own discipline called "Interaction Points" has been created for collecting all interaction points as reference workflows. The globally identified interaction points are outlined within the outline of each phase below.

Figure: Modelling of interaction points as capability patterns and process usage as activities

The picture above reflects the considerations that were undertaken in the deliverable D3.1 chapter 4. Here it is formulated that co-engineering adds a new process step as interactions whereby they can be implemented either as reviews and discussions between experts or more formalised by tool supported analysis. Therefore, for instance, the interaction point "Safety Requirements Consolidation" shown in the figure is defined as a step in the Analysis Phase that requires the involved parties to review other quality requirements, to analyse their interference in respect to SSP and to update the requirements according to the findings. This approach of defining interaction points can and will be applied to other stages in the PLC.

## 3 Use Cases

## 3.1 UC1 – Air Traffic Management [ISYS]

The AQUAS ATM use case focuses on offering innovative situational awareness services to UAVs operating in Very Low Level scenarios (city environments, mountainous terrain or areas covered by vegetation). In these cases existing surveillance technologies are often limited due to radio signal propagation issues or lack of infrastructure, resulting in air traffic that could remain momentarily or permanently hidden for the UAV pilot depending on mission conditions.

The ATM use case intends to apply alternative communication technologies, such as LTE, to facilitate the exchange of surveillance related data among small UAVs in VLL environments, and leverage flight information gathered from governmental and trans-national agencies (e.g. Eurocontrol) to enable detecting hidden air traffic surrounding UAVs.

Similar performance targets as those applying to techniques currently in use for air traffic monitoring in terms of latency and accuracy are aimed. Fulfilling such requirements while coping at the same time with security and safety constraints in embedded computing platforms that are designed for small UAVs (thus subject to additional limitations, for example, in terms of battery power consumption) is a challenge that would benefit from adopting a co-engineering approach from the first development stages. Thus AQUAS methods and tools will be applied to the development of the UTM service elements across the major demonstrator components.

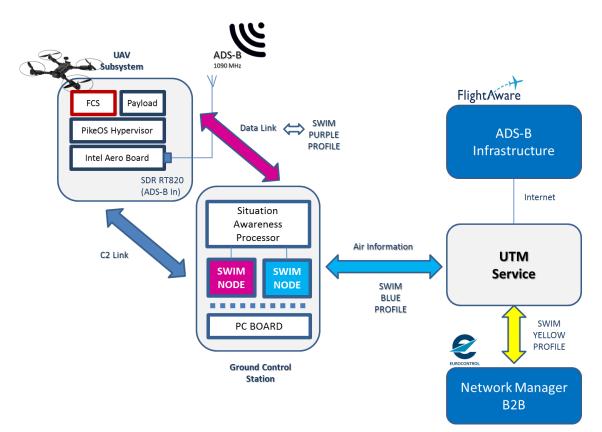

Next figure shows the overall UTM demonstrator architecture with major sub-systems involved and communication links among them.

Figure: UTM Use Case Demonstrator Architecture.

Overall, the ATM use case demonstrator consists of an airborne UAV platform, a remote control station and a server integrated in the ADS-B (Automatic Dependant Surveillance-Broadcast) ground infrastructure. Interaction with two external systems is also planned: the FlightAware ADS-B ground infrastructure and Eurocontrol Network Manager Business to Business (NM B2B) services, which will be providing information on current aircraft positions and flight plans respectively.

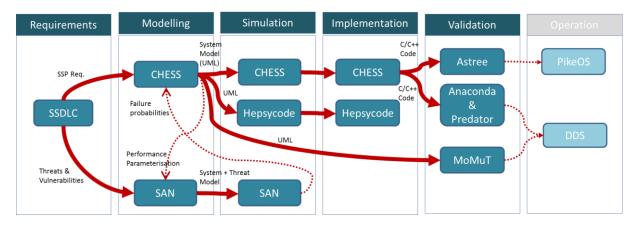

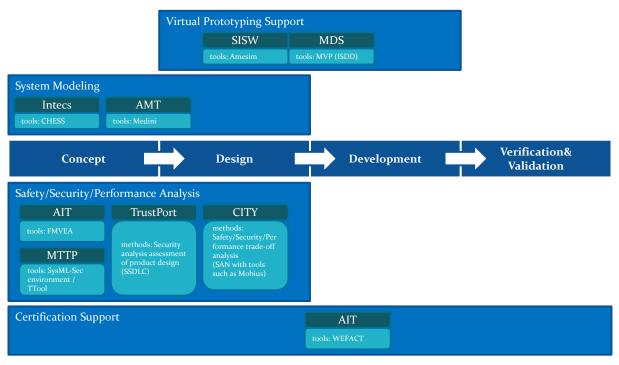

Tools supporting SSP co-engineering within the AQUAS Product Life Cycle, from requirement specification and analysis to system modelling and simulation, implementation and validation will be showcased. The following figure summarises the tools applicable at each phase and the expected use of outputs among tools participating in the tool chain.

Figure: Preliminary tool chain envisaged to support co-engineering within the ATM use case.

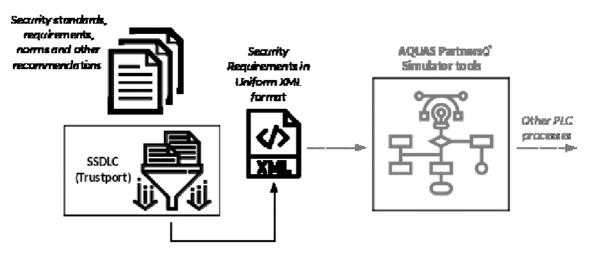

In particular, **TrustPort** plans to define a set of security requirements using the SSLDC tool. For further evaluation of Security-Performance trade-offs the TTool is being considered (in cooperation with Telecom ParisTech). Based on inputs from SSDLC, TTool permits the evaluation of the performance in two different scenarios: one with no security and one with security mechanisms. Also, the evaluation of different security mechanisms/algorithms/methods could be evaluated. For example, without taking into account penalties of the hardware platform. Outputs from the SSDLC tool will be integrated in the form of SSP requirements within CHESS and SAN models.

Then, **INTECS** proposes the CHESS tool to support the modelling of the ATM UC1 system architecture, down to the software level. The CHESS Dependability profile, embedded in the CHESS modelling language, can be used to enrich the system and software architecture model with information about error model of the system and software components, to finally enable dependability analysis, like the failure propagation analysis.

INTECS plans to investigate the usage of the aforementioned model to automatically feed the quantitative analysis proposed by City to support the co-analysis phases. Also we are investigating an extension of the CHESS dependability profile for the modelling of security threats; in this regard we are collaborating with TrustPort to understand how the information related to security requirements derived with the Secure Software Development Life-cycle (SDLC) tool can be used within CHESS.

Finally INTECS will investigate the decoration of the software architecture components with real time constraints, by using the MARTE language features embedded in the CHESS modelling language; in this case, the application of the CHESS tool support for schedulability and worst-case end-to-end response time analysis enabled by the aforementioned MARTE properties will be also evaluated.

Still in the design phase, City will use the Mobius software tool (developed by the University of Illinois at Urbana-Champaign, USA) to build stochastic activity networks (SAN) model of the ATM use case. This model will be used for combined analysis of performance and security.

An initial description of a SAN model of the ATM UC is included in Deliverable D2.2.1. The model includes a performance sub-model, which captures the effects of a variable load (e.g. due to varied number of drones communicating with ground services) on the end-to-end delays in communication between drones and the ground services and a sub-model of the impact (i.e. deterioration) of different cyber-attacks on communication delays. Upon accurate parameterisation (for which direct measurements will be required on a dedicated testbed) the SAN model will allow one to explore a wide range of situations with variable load and different attacks.

The SAN models to be used in the ATM use case will be developed using the Mobius tool on its own. No integration is envisaged with other software tools. However the City team, together with the INTECS team, intend to study whether the functionality of the dependability plug-in of the CHESS tool can be extended so as to make it possible for one to derive directly from the SysML model of the ATM UC, defined in CHESS, a stochastic model, which is functionally equivalent to the SAN model(s) developed by the City team for the ATM UC. City will assist INTECS with the functional requirements for the extension of the dependability plug-in and, in case the plug-in extension is implemented, with its validation.

Additional support for simulation and implementation closer to the target platform will be considered in the use case. In this sense, the methodology developed by **UNIVAQ** involves different aspects in AQUAS project and ATM use case. The task-level application model, to be used as input, will be provided by UCs, using Model-2Model transformations in order to adapt and extract performance metrics into safety scenarios. Connected to the demonstrator platform selection (considering Unmanned Aerial Vehicle architecture), UNIVAQ will evaluate and compare performance with respect to different processors and HW architecture technologies.

The HW/SW Co-Design methodology will be supported by external performance analysis tools provided by different partners, in order to collect system data used during the Design Space Exploration (DSE). Other Non-Functional requirements (e.g. security, power consumptions, fault tolerance issues etc.) will be considered in future works. UNIVAQ will also extend its benchmarking activities related to PikeOS, to identify possible behavioral anomalies and system vulnerabilities in terms of safety and performance constraints (e.g. spatial/timing isolation, scheduling overheads, communication bottlenecks etc.).

For validation purposes, **AbsInt** will help in assessing the safety and security of the system. AbsInt will use its tools Astrée and RuleChecker to analyse the operating system (SYSGO's PikeOS kernel) statically for finding violations of certain safety and security principles, or proving the absence of such violations. Results of these static analyses can be used as arguments for safety and security in the certification process.

In order to assess the safety of PikeOS, RuleChecker is used to detect or exclude violations of MISRA-C:2004 and MISRA-C:2012. Security properties are assessed by using RuleChecker to detect or exclude violations of CERT, CWE, and "Secure C" (ISO/IEC TS 17961) rules. RuleChecker will for all checks be run in combination with Astrée in order to exploit Astrée's sound semantic analysis of C code. Astrée will also be used to statically detect invariant assertions and invariant branching conditions. Statically decidable branching conditions can be exploited to increase system performance; while detecting invariant assertions yields further insights regarding the system's safety and security.

**BUT** will use the ANaConDA tool to strengthen safety properties related with concurrency, in particular for the OpenSplice DDS middleware, which is written in C/C++ and uses multithreaded environment. Another candidate is sDDS implemented and provided by HSRM partner.

Finally, **AIT** will apply its tool model-mutation based test case generation called MoMuT, to the ATM use case. The MoMuT family of tools derives test cases from models of the system under test for fault-based testing. The tools generate test cases that are guaranteed to detect models that contain

certain user-selectable, seeded faults. Those tests can be already used during behavior modelling for validation and improvement of the model. During test case generation, also the fulfillment of component contracts, if available, will be checked. Additionally, robustness and performance tests will be provided, to verify that certain components react safely to unexpected inputs and that certain performance goals are met with a high probability.

### 3.2 UC2 – Medical Devices [ITI]

RGB (UC2 Leader) has developed a blood pressure (BP) and neuromuscular transmission (NMT) monitoring device for hospital operating room critical care performance. The system is using very innovative technology to support the anaesthesiologist in simultaneously monitoring BP and NMT during an operating room procedure.

In the case of BP control, the system operates by delivering vasoactive drugs with the goal of reducing patient's hypertension, and precisely controlling blood pressure measurements in a patient undergoing surgical intervention in the operating room or in post-cardiac surgery in the Intensive Care Unit.

In the case of NMT control, the system will use relaxation drugs at the beginning of the operation, in the so-called induction phase, and will make sure that the patient is at the required relaxation level all along the operation, either in moderate, deep or intense blockade level; Then a second drug will be used in the recovery stage at the end of the operation.

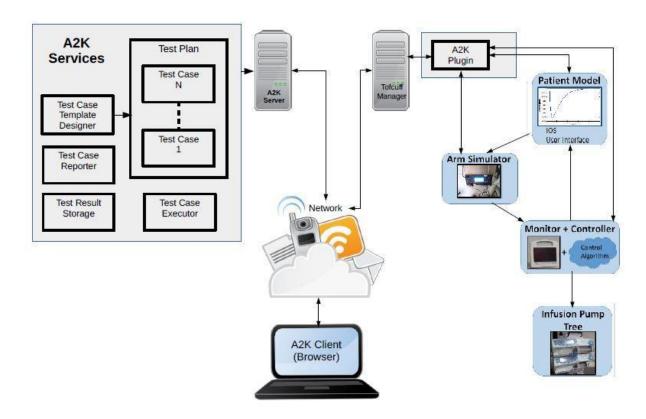

From a technical architecture view point, the Medical demonstrator is composed of the Hardware in the Loop benchmarking system, on one side, and the test environment, based on PC software, on the other, as depicted in the figure below. The Medical demonstrator is a combination of the Medical use case with established and novel methodology and tooling provided by the use case partners.

## **System Engineering Environment**

#### Methods and Tools Monitor + Controller Simulated Blood New dose Control **Quality Management** Pressur infusion Algorithm **Requirements Mng Risk Management** Arm Simulator Patient Modelling Infusion Pump Configuration Patient Model Tree **Test Cases: Functional** Blood Verification Plan Pressure values Definition 105 SW tests User Interface **Test Results** Interoperability Impact Analysis Configuration of Tests Hardware in the Loop Test Documentation, Etc...

Figure: System Engineering Environment

The Hardware in the Loop prototype (HiL) will model selected parts of the real-world demonstrator with the goal to evaluate tools and methodology that enable the evaluation of safety, security and performance implementation attributes throughout the product life-cycle.

The basic idea for the technical part of the AQUAS Medical Devices Use Case demonstrator is to virtualize a real-world (physical) demonstrator where the patient is replaced by a mathematical model that behaves as a human. In practice it is a transfer function that relates as output the changes of the physiological parameter under control, having as input the specific drug(s) infusion(s) value(s). The blood pressure controller in the picture also includes the NIBP and NMT monitors, so that in practice, together with the Infusion Pump Tree, these are the two Medical Devices that will eventually be linked and used in the Medical practice

Physical Demonstrator: The objective will be to provide an environment to be used for the Functional Verification of the system allowing with some limitations:

- Automatic execution of the Test Plans.

- Increase Requirement Traceability incorporating tools into the development process.

- Accelerate design by using tools to analyze the performance of different potential architectures.

- Increase the safety of the patient by using Hardware in the Loop System to verify the functionality of the Controller before Clinical Validation.

To implement these objectives, ITI is developing a Quality Management (QM) module for the Art2kitekt (A2K) software suite. This will act as a tool to support co-engineering tasks. The architecture of the system is shown below.

Figure: Architecture of the System

This architecture will act as a harness which will manage inputs to and outputs from the various hardware components of the demonstrator system. It will compare the measured test results to those expected and provide reports. It will also manage the relation between real and expected results in terms of the constraints provided by the various tools used during the design, implementation and test procedures.

The tools, procedures and workflows that we intend to integrate within the A2K QM are as follows:

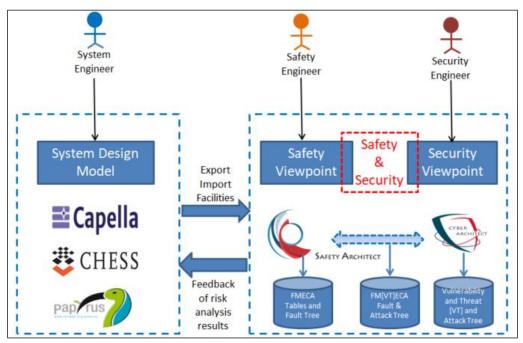

**ALL4TEC** proposes a Safety and Security co-engineering method based on Safety Architect and Cyber Architect tools, as presented in Section 4.9. The proposed method supports risk management inside product life cycles (requirement or modelling phases) and across these two phases. If system requirements or architecture models are created in partner tools based on SysML/UML model, the resulting SysML/UML models could be imported in Safety Architect for classical safety analysis, RRA002 (FMEA/FMECA tables that enables tabular linking of safety requirements to safety barriers that symbolizes modelling elements to reduce the failure propagation at system component outputs) or in Cyber Architect for Security risk analysis, RRA003 (vulnerabilities and threats modelling in tabular form with the possibility of defining dependencies). Based on the analysis results, the system architecture solution could be confirmed or rejected with the need for re-design or enhancements across product life cycles.

**AMT** will create a SysML model using medini analyze, that will allow safety and security analysis. Applicable risk analysis methods will be applied. The model might be imported into the other SysML tools.

**City** - main planned contribution concerns analysis of system requirements/specs TrustPort's contribution in AQUAS Medical use case can be security requirement definitions like sensitive data misuse, data confidentiality, integrity, availability, non-repudiation and quality of service. From the viewpoint of human factors, addressing requirements of e.g. IEC 60601-1-10, specifically about safety/security implications of: mental model the operators have of the device; cases in which the operator must intervene (clauses 5.1, 6.1. Also relevant: EN62366-1, "use error"-related clauses). The main novel aspect of this is analysis of safety concerns regarding operator intervention scenarios.

In addition, we expect to possibly contribute to:

- threat analysis from the combined safety/security viewpoints, especially regarding human contributions, as part of early interaction points;

- specification of the test plan such that an argument, possibly statistical (*cf.* D2.1.2) can be derived as to how the test demonstrates that the software is properly verified (matches specification) and/or validated (fit for purpose and safe).

Last, the City team will contribute to the planning of interaction points and study of their effectiveness, according to its role in WP3.

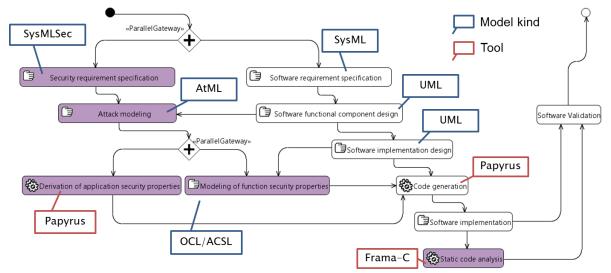

**CEA** – wish to use a combination of Papyrus modeler and Frama-C static code analyser to apply a model-based software/security co-engineering method for security properties verification. The method is described in Section **Error! Reference source not found.** In particular CEA will use Papyrus or the software architecture modelling, and the security requirements and refined properties modelling. Modelled elements will be traced and related with Papyrus traceability tools. Papyrus will also be used to generate code for the software architecture, with ACSL annotations representing modelled properties. Such ACSL annotations can be either directly generated, if properties are directly modelled, or inferred from higher-level requirements that are modelled and refined.

**BUT** - will contribute in modelling and simulation of the whole patient-in-the loop system. BUT will design and implement a complex simulation framework covering the control mechanism, drug injection pump, model of the patient and measurement device (blood pressure, neuromuscular relaxation etc). These parts of the framework will be modular and allowing to plug in real technical components. The goal is to experiment with various types of new drugs, control mechanisms and safety issues (robustness of the control mechanism in cases of malfunction of the pump or measurement device). BUT will also consider possibilities of analysing resilience of the control mechanism against errors, including errors in the input measurements. Apart from that BUT will offer its experience and tools analysis of various aspects of the use case code, including, e.g., concurrency aspects, memory safety aspects, and/or performance-related aspects. Finally, BUT will leverage its experience in computer security and, in collaboration with TrustPort, help evaluating security features of the proposed solution.

**Tecnalia** - The main contribution is to analyse the use case and to develop an assurance case by using OpenCert tool. We will include co-engineering factors to the safety cases and it will be used through the lifecycle. The assurance case provided by RGB will be modelled, considering, the safety, security and performance requirements requested by the standards use case. The assurance case model must ensure the co-engineering factors are shared among the different phases of the lifecycle.

In addition, TrustPort plan to contribute to threat analysis from the combined security/performance viewpoints, including human contributions in design, modelling and verification of product life cycle.

TrustPort's contribution in AQUAS Medical use case can be security requirement definitions like sensitive data misuse, data confidentiality, integrity, availability, non-repudiation and quality of service.

### 3.3 UC3 – Rail Carriage System [ClearSy]

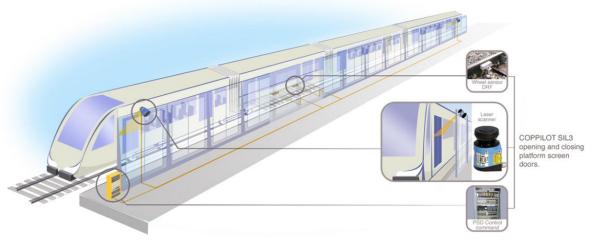

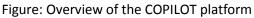

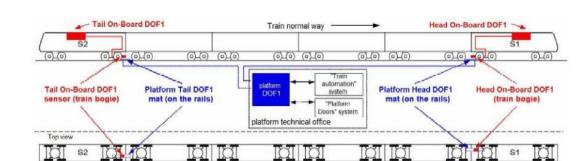

As described in WP2 D2.2, Clearsy expects advances in security, safety and performance analysis through new processes and methods applies to the COPPILOT metro doors control system. This system must achieve high safety and performance constraints. Basically, the screening doors should open when a train is stopped at the right position on the platform and its doors are opening, and the screening doors should close when a train is stopped at the right position on the platform and its doors are opening and its doors are closing.

The COPILOT system design approach mainly rely on formal methods cascading to code generation (development), testing, commissioning and exploitation (return or experience as inputs to system improvement).

Design and analysis tools chalenges are first to ensure always faster and safer controllers but also to bridge domains with system level and consider systems interactions. As illustrated below (only for the ground sensing part), the COPILOT system dynamically interacts with many other systems (rolling stock, other ground systems, sensing...) of sometime variable configurations, leading to adress relatively high operation complexity, which must be captured by tools and not only considered as boundary conditions.

Ш D

Figure: COPILOT interaction with train

I 101

Figure: Train dynamics and bus signals

Figure: Doors openning State machine

So, the tooling challenge will be to improve state of the art approaches used by Clearsy, ranging from the embedded software development to etended virtual system SSP validation.

BUT will investigate new tools interactions to automatically analyse selected critical safety and performance code features and checking the absence of critical code errors whenever new code is introduced or changes are required after an interaction point.

It will be achieved through

AQUAS

- static analyses with tools like Predator, 2LS, or Ranger/Loopus using the approaches of abstract interpretation, (bounded) model checking, and SAT/SMT solving.

- dynamic analyses with tools like ANaConDA and Perun use extrapolating dynamic analysis, noise injection, and statistical analysis.

The BUT tools (Predator/Forester/2LS, ANaConDA, Ranger/Loopus and Perun) and their planned extensions will stay generic but with a stress on modularity and efficiency needed at interaction points, and they will be particularly optimized and validated for the use case.

CEA activities will investigate specifications translation from B0 into ACSL specifications analyses of security properties through static code analysis (WP plug-in of Frama-C tool) and relate static code analysis to system/software models. CEA aims too achieving tool cooperation by import/export of models in Papyrus UML/SysML and new properties modelled as annotations in Papyrus UML/SysML model and code generated (with annotations) for static code analysis. CEA aims also at developing collaboration with MTTP on SysMLSec integration and partner tools involved in CHESS to promote interoperability through Papyrus.

**MTTP** will explore the use of the SysML-Sec approach (supported by the free and open source toolkit "TTool") in order to verify the security (and safety, and performance) requirements on the system. The analysis will be performed on the HW/SW partitioning stages of SysML-Sec. More specifically, MPPT will identify security and safety requirements, identify and model attack trees, model the functional and architectural view of the system to finally propose and evaluate system safety and security requirements.

**SISW** will contribute to the behavioural/time-domain system analysis investigations to extend SSP analyses practices. These analyses will involve various tools interactions (controls runtimes, physical models, requirements...) at different stages of the product life cycle (development an operations) and will involve techniques like time domain system simulation combined with SSP requirements. Along with the use case leader, these investigations should achieve better knowledge on how complex CPS design practices could be improved to achieve higher SSP. Tools interactions will be investigated using as possible standard interfaces like FMI, Sfunction or any other relevant interfaces.

**Trustport** aims at investigating the transformation and interactions of security and safety requirements created from security standards, norms and best-practices to use-case PLC tools and provide final set of security requirements to compliance process. Trusport aims at developing collaboration with BUT regarding test scenario definitions.

### 3.4 UC4 – Industrial Drive [AMT]

In UC4 a virtual HW prototype of an industrial drives system will be created that shall be used to verify performance constraints together with safety and security requirements for a representative set of scenarios. The scenario considers the development phases concept, design, development and validation. Operation and retirement phases are not in the scope of this use case. See deliverable D2.1.4 for a detailed description of this use case. D2.2.4 provides details on the architectural and processual requirements.

The following sections describe the process followed by the use case with a focus on the tools and their interaction from the perspective of co-engineering the three quality aspects safety, security and performance.

### 3.4.1 Process Definition

The SAG system development generally adheres to standards IEC 61508 for functional safety and derived standard IEC 61800 (Adjustable speed electrical power drive systems). The process defined within AQUAS must be compatible to the latter standard. Additionally, it should follow the security guidelines for the industrial domain set out by the international standard IEC 6244300 to provide a solution that is secure-by-design.

To ease the evaluation of co-engineering, the approach in UC4 is to limit the scope of a full-blown product life cycle to a subset and later integrate successful results into the full product life cycle.

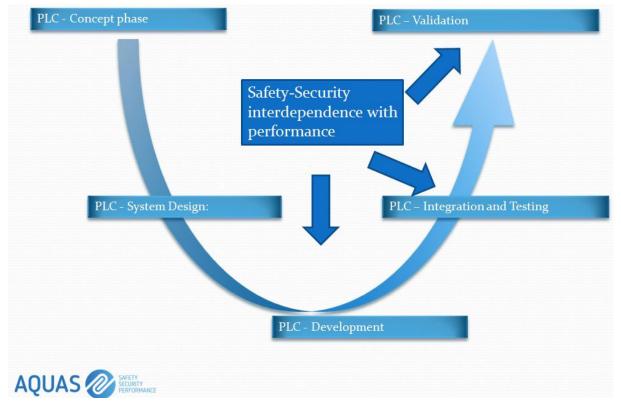

Figure: Overall life-cycle of UC4

The above figure depicts the overall life-cycle method with additional tracks indicating safety, security and performance standards and guidelines. It serves as base life-cycle for the industrial drives use case demonstrator.

Below diagram breaks the product life cycle down into activities from the different development disciplines and maps them to the tools from the AQUAS partners that are applied in this use case. The central data for interaction throughout the use case is a system model in SysML that is annotated with quality attributes and a requirements model for safety, security and performance requirements. These models are initially created and maintained in medini analyze and can be exported to other tools, e.g. INTEC's CHESS tool, which can provide additional supportive quality criteria for balancing the architecture. The results of functional safety analysis lead to the addition of safety functions in the design, and additional design requirements, which can be traced with medini analyze in each product life-cycle phase.

It is desirable to enhance the current flow with features that enable a balancing of safety, security and performance. The more detail is provided to the balancing mechanisms (e.g. implementation-, timing-, area-costs of safety functions) the higher is the accuracy for hitting the optimally balanced architecture for all quality aspects.

Figure: Activities of the UC4 product life cycle mapped to AQUAS partners' tools

As mentioned above, UC4 limits its scope to the following activities and their interaction in the product life cycle.

**System Modelling:** The methodology elaborated in SESAMO shall be enhanced with performance considerations in early stages. medini analyze is used to relate selected security and safety mechanisms to requirements. CHESS is used for timing analysis. Particularly, the CHESS tool can be extended with code generation features and WCRT (worst-case response time) analysis capabilities.

**Safety-Security Analysis:** Evaluate applicability of the FMVEA (Failure Mode Vulnerability and Effects Analysis) for combined safety and security analysis and compare it to other suitable approaches (e.g. SESAMO's Security FMEA).

**Safety-Performance Analysis:** Evaluate feasibility for time-domain behavioral analysis of the combined virtual controller and the virtual physical system.

**Virtual Prototyping:** Support the verification of safety features and other quality aspects. Implement a seamless flow from System Level Model to the Virtual HW Prototype. Provide a platform that allows direct comparative analysis of Virtual Prototype vs. FPGA approach and combined controls models and virtual physical environment as well as combined virtual platform and virtual physical environment.

**Certification Support:** WEFACT as framework for supporting a general assurance case covering all relevant dependability attributes (safety, security and performance).

The product life cycle of UC4 maps to the analysis and realization phase of the AQUAS methodology, the operational phase is not in the scope of this use case. The UC4 product life cycle has been modelled using the process building blocks from the AQUAS methodology (see section 2) as delivery process in the EPF model using EPF Composer. The following sections describe important aspects of the delivery process and the deviations from the AQUAS methodology. For a more detailed description and navigability between the process artefacts, please refer the additionally delivered EPF model and generated process website.

Version 1.0

### Analysis Phase

The analysis phase of UC4 is separated into a concept and a design phase.

The goal of the Concept Phase is to collect basic system information, derive functional safety and security requirements, as well as creating preliminary architecture. Tools and methods applied for this phase usually capture system information in an organized way (spreadsheets, databases) that allows the definition of dependencies and enables tracing of requirements and artefacts throughout the process. medini analyze is used for requirements engineering, safety analysis (FMEA, FTA), security analysis (Attack Tree, Security-FMEA) and for system modelling (SysML).

Figure: Concept phase of UC4

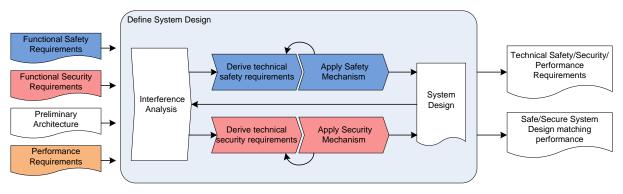

The System Design phase consists of two activities, Define System Design and Hardware and Software design.

Figure: Product Life-Cycle: System Design

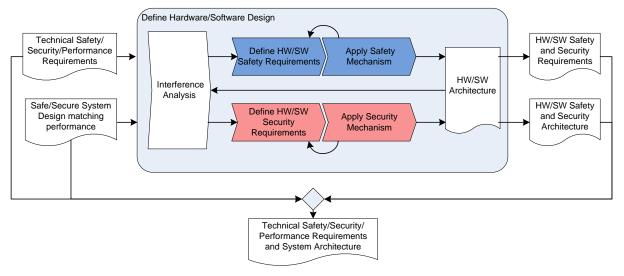

The purpose of the System Design Phase is to create technical safety, security and performance requirements as well as a safe and secure system design that is aligned to performance requirements. Safety and security mechanisms are applied concurrently at first, but also balanced with respect to performance requirements. Each applied mechanism (e.g. safety building block or security building block) shall have its own performance attributes and thus enabling a way of performance-aware interference analysis.

Figure: Product Life-Cycle: Hardware and Software Design

With the technical safety/security/performance requirements and a system design in place, the next step is to decide which parts of the system are to be implemented in SW or HW. The flow applied is basically the same as the one for system design, but ending with technical safety/security/performance requirements and a system architecture including the system distribution into SW/HW.

### **Realization Phase**

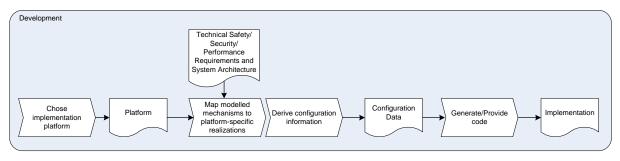

Figure 11: Product Life-Cycle: System Development

In the development phase, the modelled system architecture with its safet/security mechanisms is mapped onto a chosen implementation platform. Ideally, that platform has code generation capabilities inhibiting the need of manual coding, thus saving costs and efforts.

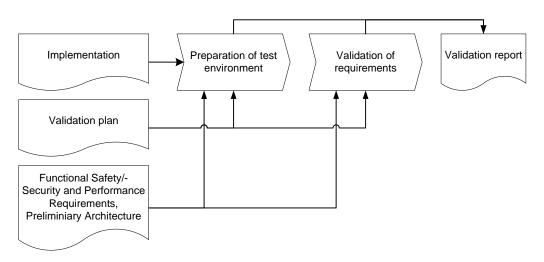

Figure: Safety and Security Validation

In phase Safety and Security Validation requirements are validated against the implementation. Note that for the industrial drives demonstrator a specific testing phase is omitted due to the experimental nature of virtual prototyping.

### 3.4.2 Tasks and Activities

In order to avoid inconsistencies please have a look at the list of partner contributions, which can be found in D2.2.4 – Demonstrator Architecture, chapter 2.

Nevertheless, a short overview is provided hereby. Following tasks related to tooling are expected for UC4 (please note that this list may evolve during the implementation phase and should be considered as living content):

- Requirements modelling

- SysML concept architecture model

- FMEA/FTA

- Security-FMEA/Attack Tree Analysis

- o FMVEA

- Timing analysis of the system (with model imports from Medini Analyze) in CHESS

- Interference analysis for safety/security/performance (at various PLC points see D2.2.4 for an interaction points example, as well as D3.1 for a list of expected interaction points in UC4)

- WEFACT modelling for certification support

- SAN modelling (e.g. with Mobius) for safety/security/performance system validation in early phases

- Virtual prototyping support (SystemC) by MDS with MVP tool

- Virtual prototyping workflow with ISDD (MDS) (safety, security, performance)

- Virtual prototyping workflow based on SysML-sec (TTool) (safety, security, performance)

- Electronic motor modelling with Amesim coupled to the SystemC-based virtual prototype

• Secure Software Development Lifecycle (SSDLC) for security requirements engineering and security testing/assessment, as well as supporting security activities during the development process

### 3.4.3 Methods and Tools

The current tooling of UC4 provides some integration that has been implemented for the SESAMO project between medini analyze and CHESS. This included the

- Hazard and Threat Analysis in medini analyze,

- derivation of functional and technical safety/security concept by formulating requirements based on qualitative fault tree analysis that was done on a SysML model,

- export of the SysML model to CHESS in order to do some complex Worst-Case-Execution-Time analysis that resulted in more requirements that were later be exported back to medini analyze in order to show traceability to the system design model in SysML.

In AQUAS there are some potential enhancements planned, that shall be addressed to better support interaction between disciplines and integrate quality analysis results in one common database for review and analysis in the interaction points.

The exchange of SysML models between CHESS and medini analyze shall be enhanced, on the one hand the exchange of diagrams and their layouts shall be supported. Additionally, re-importing models from CHESS into medini analyze would be comfortable, making a roundtrip integration possible: Changes on the system model in CHESS could be fed back to the SysML models in medini analyze. In CHESS, the support for incremental updates could be improved, so that, when the system architecture design in medini analyze requires changes, not most of the separation of the system model into HW/SW in CHESS needs to be redone.

With medini analyze and CHESS being used across life-cycle phases, the other tools need to integrate with the data taken from these two tools. medini analyze will provide requirements engineering and system modelling, CHESS will provide modelling and simulation with special focus on timing analysis.

### 3.4.4 Interaction Points

A detailed example for an interaction point is described in D2.2.4 – Demonstrator Architecture, chapter 1.3 – Product Life-Cycle. Furthermore, the current list of expected interaction points for other PLC phases can be found in D3.1.

### 3.5 UC5 – Space Multicore Architecture [TASE]

For UC5 Thales Alenia Space in Spain is developing an application that will run on a multi core platform which is certified by the ESA for flight purposes.

The selected platform is a Gaisler GR712RC board which incorporates a Leon 3 dual core processor. In the scope of AQUAS the software aspect of this platform will be studied in order to study the interdependencies between Safety, Security and Performance.

The software will perform tasks like memory scrubbing, watchdog functions and telemetry and telecommands receival/sending, which will run in separate cores in the defined platform. The

possibilities of locks, interdependencies and inconsistencies due to concurrency problems will be the main focus.

Requirements for each aspect have been defined and subjects like achieving the target performance while maintaining the safety and security aspects of the application intact will have to be studied.

Figure: Stages in UC5

AQUAS partners will contribute to this study with the proposed methodologies and tooling.

**INTECS**: Provide support for the modelling of the SW architecture and associated timing properties.

To be used to enable schedulability, worst-case response time analysis.

CHESS information could be used to instrument the TimingProfiler tool.

Collaboration with All4Tec. Understand safety/security related information that can be exchanged between the two tools.

**TECNALIA**: Analyze the use case and to develop an assurance case by using the OpenCert tool.

OpenCert is a product and process assurance/certification management tool to support the compliance assessment and certification of safety-critical systems.

**MDS**: Participate in the formalization of a workflow for the balancing of Safety, Security and Performances.

Show the capabilities of the ISDD© which is a platform integrating each process of a project: Specification, Design and Documentation.

**ITI**: A2K tool upgraded to simulate, generate code, and monitor dual-core, shared memory, Leon processors running RTEMS.

A2K tool upgraded to provide sensitivity analysis of task schedulability to task timing parameters.

**BUT**: BUT will leverage its long-term experience with hardware-accelerated solutions of various computationally expensive tasks to evaluate the efficiency of the considered system architecture of the use case and to investigate possible optimizations of the proposed solution using, e.g., specialized hardware.

BUT will contribute tools and methods for detecting concurrency defects mainly through dynamic analysis using its ANaConDA framework.

TRT: State of the art done on performance verifications techniques for multicore GR712RC

Coordination meeting with ITI.

Ongoing: Work on detail software architecture of the case-study, definition of methodology for FPGA.

UNIVAQ: Introduced Safety (Sa) and Performance (Pe) constraints into the Hepsycode Methodology

Extended the Design Space Exploration (DSE) to consider processes/tasks/threads partitioning (with HPV SW-partitions)

Analyzed different HW/SW multi-core LEON3 scenarios.

**SYSGO**: SYSGO will contribute to the AQUAS project its safe and secure real-time hypervisor PikeOS, which will be used to examine novel techniques for improving safety, security, and performance in combination, by trying out new static analysis techniques. In the context of this use case, SYSGO will explore to create its own special analysis tools especially suited for specific problem classes with the PikeOS hypervisor, where we do not have any tool available.

**HSRM**: Integrating verification and testing. Methods and languages for Worst Case Response Time (WCRT). Layered overall architectural design of a real-time microkernel.

**ABSINT**: Adapted TimingProfiler(TP) tool to UC5. Supplied all partners with TP and training. Support partners in usage of TP.

**ALL4TEC**: Integration of Safety Architect tool with Papyrus/CHESS tool to import system architecture model. Safety analysis (FMEA/FTA) on the UC software architecture model. Evaluate Safety Architect and Cyber Architect tool integration for combined safety and security analysis.

Aside from the SW development, as a sub-use case, **TRT** will develop an activity involving an FPGA which they will coordinate and will have contribution from several partners under the scope of UC5.

## 4 Tools

This chapter describes the tool-specific functionality required to support the co-engineering process according to the AQUAS methodology. The descriptions focus on tool features supporting the interaction of domains and disciplines, e.g. in the area of tracking process progress, data and artefacts, and particularly interaction points, where cross-domain and cross disciplinary analyses must be executed to realize safety-security-performance analysis, supporting system design space exploration and trade-offs.

Providing this functionality requires tool integration in many cases. The tool descriptions reference back to the delivery process of the use cases, where applicable.

### 4.1 System Modelling and Analysis of Quality Criteria [AMT]

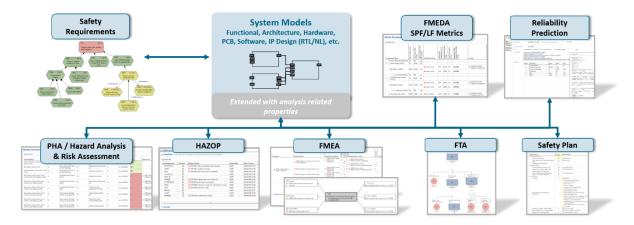

AMT is supporting the safety and security co-engineering by bringing in its tool medini analyze, a toolset supporting the safety analysis and design for software controlled safety related functions. As depicted in the figure below system models that represent the design of these functions are enhanced by properties that support the different analysis methods that are applied in the context of safety considerations, like Hazard and Risk Assessment (HARA), Fault Tree Analysis (FTA) or Failure Mode and Effect Analysis (FMEA).

Figure: Safety related analysis in medini analyze

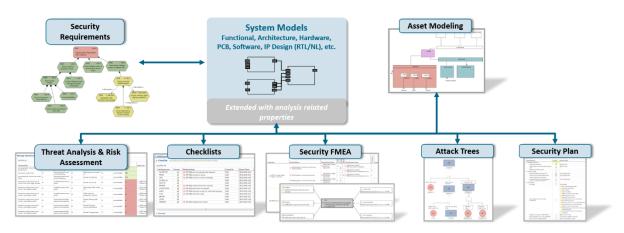

Beside the safety aspects medini analyze supports the analysis of security quality criteria based on the same mentioned system models (see figure below). It allows for the modelling of assets that might be potential goals for a security breach. These breaches can be examined by conducting an Attack Tree Analysis that result in Attack Paths describing potential scenarios how the asset can be attacked. These scenarios are assessed in respect to the criticality by applying a Threat Analysis and Risk Assessment.

Figure: Security related analysis in medini analyze

In order to support the different requirements coming from the safety standards in the different domains (e.g. Medical or Industry) and additionally to support the various methods that are applied in the area of security medini analyze will be extended by the concept of so-called domain profiles. These profiles introduce the domain specific terminology, the different risk graphs and different analysis methods in a highly adaptable manner. This is especially important in the security domain because here the standards are currently under development and not yet finalized.

Examples for the differences in standards and methods supported by domain profiles are:

- Criticality Levels (SIL, DAL, ASIL)

- Analysis Methods like

- Hazard and Risk Assessment

- o Threat Analysis

- Support for threat model classification according to STRIDE [STRIDE]

- Fault Tree Analysis

- o Attack Trees

- o Failure Mode and Effect Analysis

- Support for Hardware Metrics (Safe Failure Fraction, Single Point Fault Metric, Latent Fault Metric, etc.)

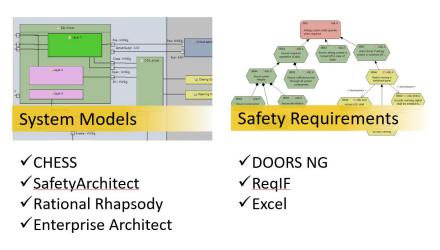

The potential interaction points that medini analyze supports consist in the exchange of system design models and requirements.

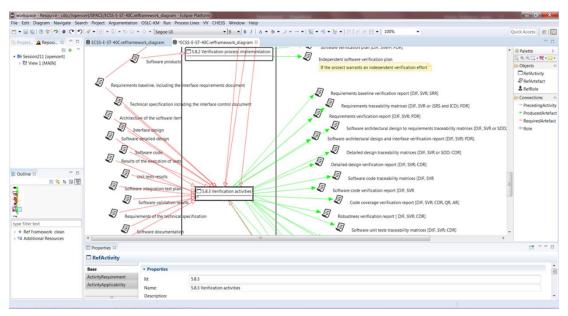

Thus various interfaces to other tools to support this exchange of models exist and will be extended in the AQUAS project. To be emphasized, in particular, are on the one hand side the interfaces to the CHESS platform that were initially developed in the context of the SESAMO project and that are planned to be extended and on the other hand the interface to DOORS NG that was developed within the AQUAS project for UC2.

The following table shows the proposed specific functionalities of medini analyze to be addressed in AQUAS.

| PLC phases<br>addressed      | Tools Interactions<br>to be implemented                         | Domains<br>interactions<br>Identified<br>interaction point                                                     | Expected SSP<br>benefits                                                         | Use case            |

|------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------|

| Concept and system<br>design | medini analyze,<br>Papyrus/Chess,<br>Safety Architect,<br>SSLDC | Safety and Security<br>analysis with medini<br>analyze and<br>exchange of<br>requirements and<br>system models | Tools support to<br>improve Safety,<br>Security properties                       | UC2 - Medical       |

| Concept and system<br>design | medini analyze and<br>Papyrus/Chess                             | Safety and Security<br>analysis with medini<br>analyze and<br>interactions with<br>CHESS                       | Tools support to<br>improve Safety,<br>Security and<br>performance<br>properties | UC4 –<br>Industrial |

## 4.2 Co-Design and Implementation of Safety and Performance [ITI]

ITI is contributing to the AQUAS project objectives by providing the foundations in the development processes to execute co-engineering activities efficiently, especially in the domains of safety and performance. These processes will in particular define and implement the mechanisms of interaction between the different tools and technologies used in the AQUAS co-engineering tasks. In other

words, ITI is providing the technical support, expertise, software and work-flows to facilitate the variety of interaction points that will emerge during the project.

At this stage in the project most of the interaction points are still under discussion and not yet well defined, so we are adopting an agile, flexible approach to their design and implementation processes. These activities will focus on researching and identifying the ways and mechanisms of allowing partners' tools to perform co-engineering analysis of their models and design resources. This will be driven by the outputs of Work Package 3 (methodology) and of course the ongoing work in each use case. An important main goal is to facilitate tool interactions that will enable analysis and modeling to check validation of the associated requirements.

ITI is also exploring the possibilities of Design Space Exploration where the engineer can try out different system configurations to see how trade-offs between safety, security and performance (SSP) artifacts and metrics affect the final system design. This task of course depends strongly on the definitions of the appropriate SSP metrics and how these relate to system design parameters. These quantities are now beginning to emerge from the other work packages in the project.

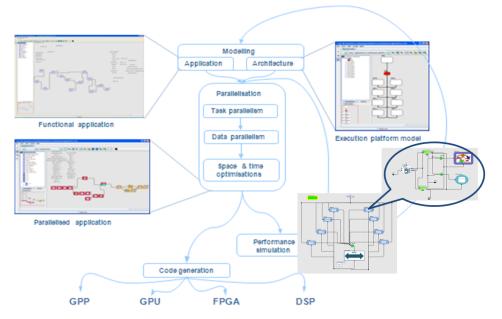

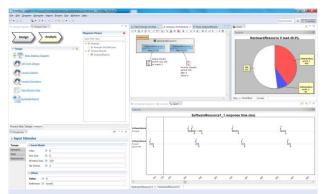

ITI is using its Art2kitekt (A2K) tool in two use cases: UC2 (medical devices) and UC5 (space multicore). A2K is a tool that enables modeling, analysis (timing, power, etc.), simulation, code generation, monitoring, and quality management of heterogeneous cyber-physical systems. In UC2, A2K is being used as a test manager for the medical hardware-in-the-loop. In this application A2K will provide stimuli to the system under test, collect system outputs, and compare these to desired safety and performance results. A2K will also interface with other tools as a manager and implementer of the (to be defined) interaction points.

In UC5 A2K will be used for modeling and timing analysis of the multi-core architecture. We are interested in exploring how aspects of safety and performance are related to different deployment conditions of, for example, the distribution of tasks to processor cores, the data communication between the cores, and use of shared resources. This is a good example of the close relationship between design and implementation in a safety and performance context.

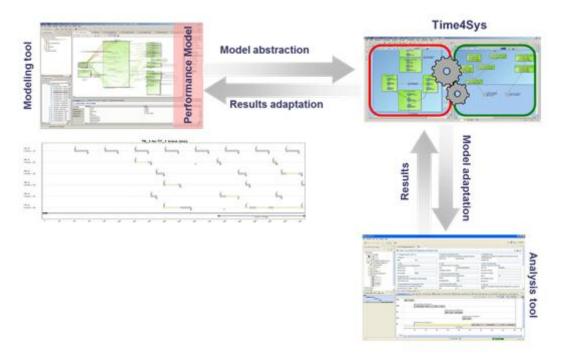

At the present time ITI is currently collaborating with the partners Absint and BUT in building some co-engineering demonstrator applications. With Absint ITI is planning to use their TimingProfiler tool in conjunction with A2K to provide accurate estimates of the worst-case execution times of software tasks. These timings will be imported into A2K to enable timing, schedulability and sensitivity analyses to be performed. ITI is also exploring how to integrate BUT's static code analysis tools (Anaconda & Perun) into A2K to provide safety and performance information during the design and implementation processes.

Regarding other tool interactions, as the project develops ITI will take into account the various information that needs to be collected in the design models and analysis tools that should be collected for enabling co-engineering support. Beyond model types and formats, semantic gaps, data repositories, management, communications, and dependencies are all being addressed, in an agile fashion.

| PLC phases<br>addressed | Tools Interactions to<br>be implemented   | Domains interactions<br>Identified interaction | Expected SSP<br>benefits                         | Use case |

|-------------------------|-------------------------------------------|------------------------------------------------|--------------------------------------------------|----------|

|                         |                                           | point                                          |                                                  |          |

| Concept and system      | A2K – simulation,                         | Safety and                                     | Rapid exploration                                | UC5 -    |

| design                  | timing analysis & code                    | Performance.                                   | of system timing                                 | Space    |

|                         | generation.<br>BUT Code Analysis<br>Tools | Sensitivity analysis.                          | performance<br>under different<br>conditions and |          |

|                         |                                           | Design Space                                   | configurations.                                  |          |

|                         | Absint Timing Profiler                    | Exploration                                    |                                                  |          |

|                         |                                           |                                                |                                                  |          |

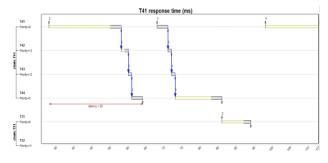

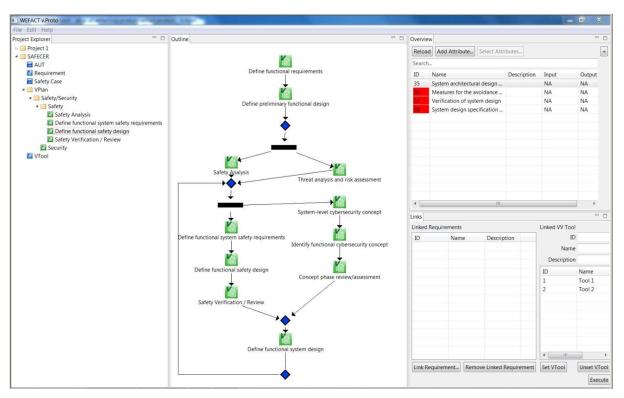

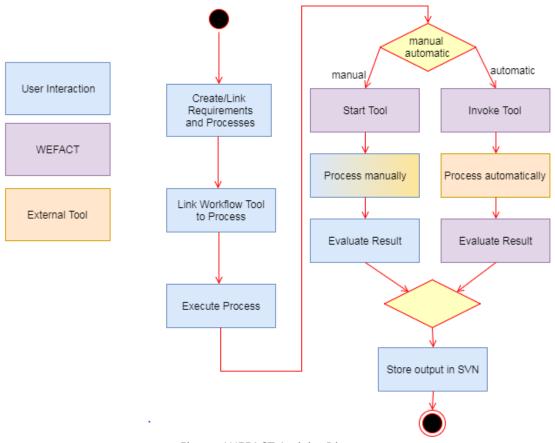

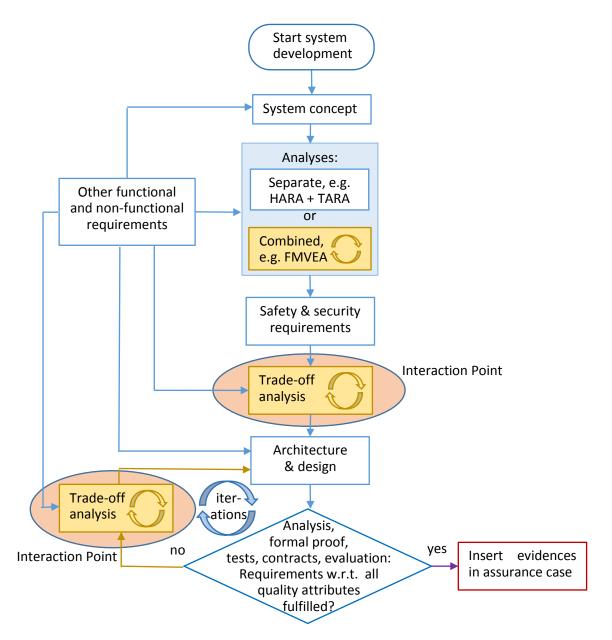

|                         | A2K Test Manager                          | Interaction of security                        | Hardware-in-the-                                 | UC2 -    |